Introduction

Silicon photonics has rapidly advanced, leveraging mature CMOS fabrication technology to deliver highly integrated optical circuits. However, like their electronic counterparts, these photonic integrated circuits (PICs) are sensitive to fabrication variations. Active tuners and controllers are essential to compensate for these imperfections and optimize performance. Taking this a step further, programmable PICs use these tuners to completely reconfigure the circuit functionality, much like field-programmable gate arrays (FPGAs) in electronics. A single generic programmable PIC can then realize a wide variety of functions, accelerating the design and prototyping process.

This tutorial explores a novel programmable silicon photonic circuit based on a hexagonal waveguide mesh architecture. We'll delve into the hardware design, building blocks like optical gates and ring resonators, and demonstrate advanced functions like coupled-resonator filters.

Hardware Architecture

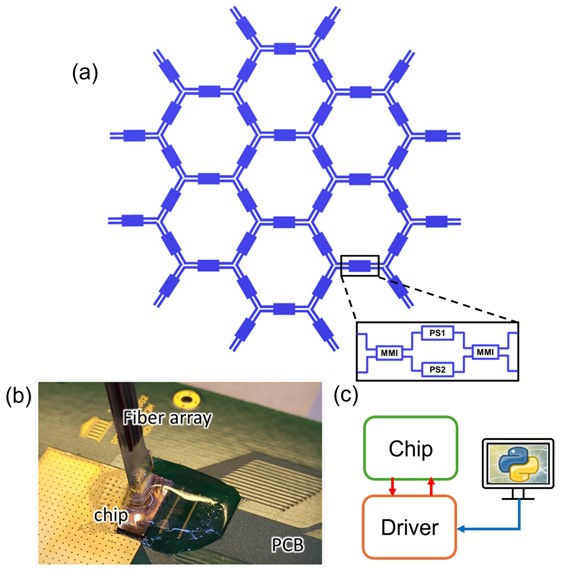

The programmable PIC is constructed as a hexagonal mesh of seven cells, with each cell containing six 2x2 Mach-Zehnder interferometer (MZI) gates, resulting in 42 optical gates total. Each MZI gate arm has a thermo-optic phase shifter, providing 84 actuation tuners across the entire chip.

As shown in Figure 1(a), the MZI gates can be configured as either a "bar" state where light passes through, or a "cross" state where it is routed orthogonally. By adjusting the phase shifters, the power coupling ratio between the two paths is precisely tunable between 0 and 1. Additionally, the common phase response is also controllable.

The chip is fabricated in IMEC's iSiPP200 process, utilizing local undercut for the heaters to enable compact integration. It has 24 optical input/output ports accessible via fiber arrays coupled through grating couplers, as depicted in Figure 1(b). The phase shifters are wire-bonded to a printed circuit board and driven by a multi-channel current driver controlled by software (Figure 1(c)) to configure the desired circuit functionality.

Optical Gate Performance

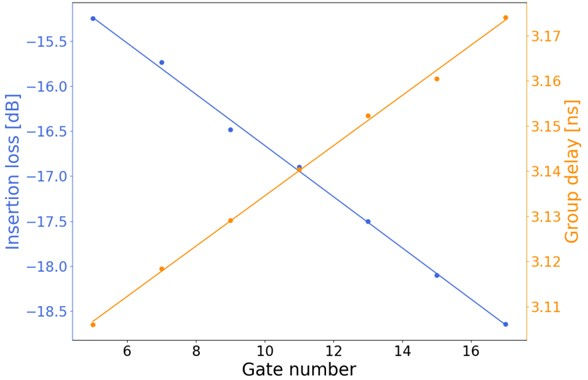

The fundamental building block is the 2x2 MZI gate, so characterizing its performance is critical. This is done by configuring various delay lines with different path lengths using the gates in bar or cross states. Since the delay lines loop back to the same input/output ports, it eliminates measurement variations across ports.

Figure 2 shows the insertion loss and group delay increase linearly with the number of gates in the delay line path. The extracted metrics are an insertion loss of 0.28 dB and a group delay of 5.5 ps per gate at 1550 nm wavelength.

Hexagon Unit Cell: Ring Resonator

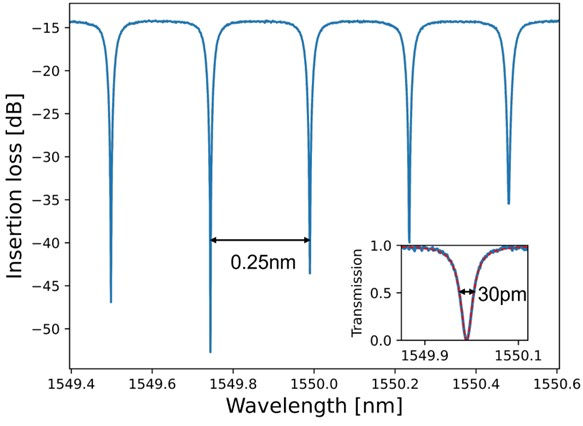

The hexagonal cell is the smallest unit that can form a ring resonator, a key component for filtering and other applications. By setting five gates to the bar state and adjusting the sixth gate's coupling ratio, a ring can be critically coupled.

The measured transmission spectrum in Figure 3 reveals a free spectral range (FSR) of 0.25 nm, corresponding to 31 GHz, and a loaded Q factor around 51,666 when critically coupled. This Q translates back to the 0.28 dB/gate loss, matching the delay line measurements.

Two-Ring Coupled Resonator Filter

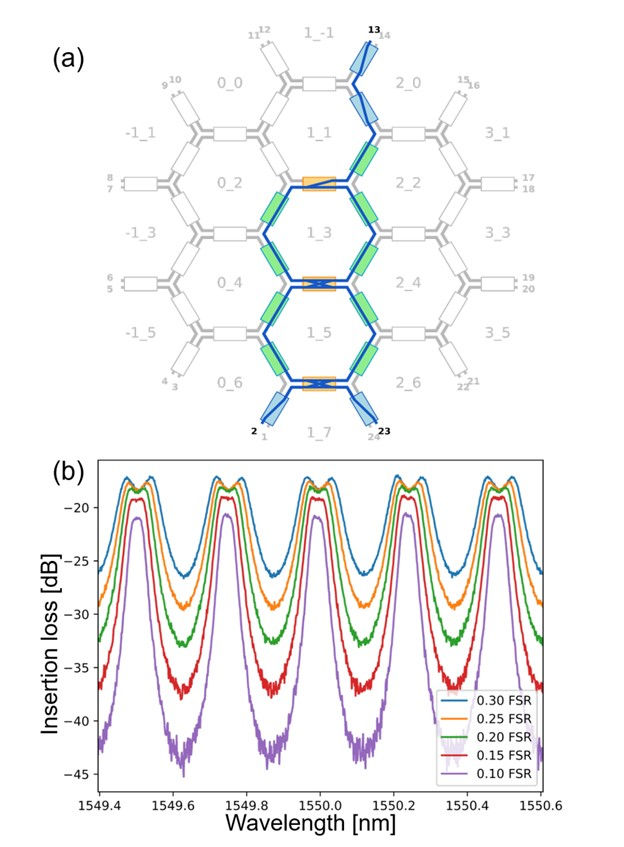

Extending to more complex functions, we can construct coupled resonator filters by precisely adjusting the coupling between rings and their phase relationships. As an example, Figure 4(a) shows the configuration of two coupled rings to implement a Type-I Chebyshev band-pass filter with tunable bandwidth.

The measured transmission spectra in Figure 4(b) depict the band-pass filter response between input port 2 and drop port 13. When the passband width is 0.1 FSR, an extinction ratio over 20 dB is achieved between the pass and stop bands.

This programmable PIC platform leverages a compact hexagonal waveguide mesh architecture with low-loss, high FSR components like rings and MZIs. It allows synthesizing advanced filter shapes and functionalities by software-configured waveguide circuits. Further applications include reconfigurable MZI lattice filters, multi-port switches, and programmable power distribution networks.

Conclusion

Programmable photonic integrated circuits unlock new capabilities reminiscent of FPGAs in electronics. The compact silicon waveguide mesh demonstrated here is a powerful hardware platform enabling the prototyping and deployment of dynamically reconfigurable optical signal processing functions on a single chip. As silicon photonics continues advancing, such programmable architectures will play a pivotal role in realizing sophisticated multi-purpose PICs for communications, computing, sensing, and beyond.

Reference

[1] Y. Zhang et al., "A compact programmable silicon photonic circuit," in Proc. of IEEE Photonics, Ghent, Belgium, 2024, pp. 1-6.

Comments