Introduction

The explosive growth in data traffic fueled by 5G, Internet of Things (IoT), cloud computing, and data centers has necessitated research into higher transmission capacities for optical networks. Multilevel coded transmission formats like Pulse Amplitude Modulation (PAM) and Quadrature Amplitude Modulation (QAM) are of particular interest due to their increased spectral efficiency. However, generating high-symbol-rate multilevel signals electronically while maintaining linearity poses significant challenges. This tutorial discusses the design of a high-performance InP Double Heterojunction Bipolar Transistor (DHBT) linear modulator driver capable of delivering a 3 Vppd PAM-4 output swing at 90 GBaud.

InP DHBT Technology and Modeling

The modulator driver is implemented in the III-V Lab's 0.5 μm InP DHBT technology featuring cutoff frequencies (fT/fMAX) up to 380/520 GHz (Figure 2) and a breakdown voltage of 4.2V. As shown in Figure 4, InP DHBTs demonstrate superior high-frequency and linearity performance compared to silicon-based technologies, making them attractive for high-symbol-rate large-swing drivers.

Accurate DHBT modeling is crucial for reliable IC design, especially at millimeter-wave frequencies where parasitic effects become significant. The conventional deembedding procedure tends to overestimate device parasitics, leading to inaccurate predictions. An improved electromagnetic (EM) simulation-based approach is proposed to extract the small-value external parasitic elements (Figures 5 and 6). This method provides better estimation of canonical cascode gain, stability factor (Figure 8), and the driver's gain response in the 50-110 GHz range, enabling more precise IC design choices.

Linear Driver Design

The linear driver employs a fully differential lumped architecture (Figure 11) with a preamplifier for input matching and a high-gain output stage. The output stage leverages a self-peaking technique (analyzed in Section III.A.2) using a paralleled-transistor cascode with emitter degeneration. This approach boosts the gain-bandwidth product while maintaining large linear output swings (Figure 9).

The self-peaking mechanism stems from the synergistic effects of emitter degeneration and transistor capacitances (Equation 2), providing high-frequency gain enhancement. Optimal transistor dimensions and degeneration resistances are chosen to position the peaking frequencies (f2 and f4) within the desired bandwidth while mitigating impedance matching degradation from excessive transistor capacitances.

The preamplifier features a linear cascode amplifier with custom emitter degeneration for common-mode rejection. The output stage utilizes a two-paralleled-transistor differential cascode with 7 μm common-base and 10 μm "common-emitter" DHBTs for optimal gain-bandwidth product and linearity. Inductive peaking networks (Figure 12) further extend the bandwidth and improve output matching.

Experimental Results

The linear driver chip (Figure 13) exhibits a measured bandwidth exceeding 110 GHz with 13 dB of peaking gain at 95 GHz (Figure 15a). Input and output return losses remain below -10 dB up to 92 and 95 GHz, respectively, demonstrating wideband impedance matching. The reverse isolation (S12) is below -35 dB, ensuring stability.

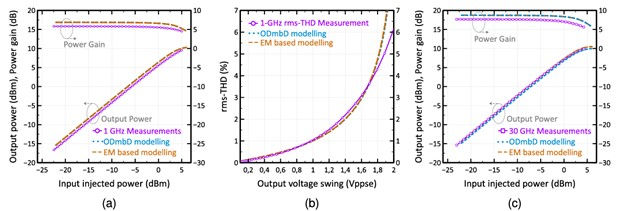

Large-signal continuous wave measurements at 1 GHz show a 9.1 dBm (3.6 Vppd) output power at 1 dB gain compression with 5.8 dB gain (Figure 16a). At 30 GHz, the gain increases to 7.2 dB due to peaking. The RMS total harmonic distortion is 2.7% at 3 Vppd output swing (Figure 16b), highlighting the driver's excellent linearity.

Digital PAM-4 measurements at 75 and 90 GBaud reveal clear eye openings (Figure 18), even without digital signal processing (DSP) or post-processing. EM-circuit co-simulations accurately predict the measured small-signal, large-signal CW, and digital PAM-4 performance, validating the improved modeling approach (Figures 15, 16, and 19).

Conclusion

This tutorial presented the design and characterization of a high-performance InP DHBT linear modulator driver for next-generation optical communications. The driver leverages an improved EM-based DHBT modeling approach and a self-peaking output stage to deliver a 3 Vppd PAM-4 output swing at 90 GBaud with a bandwidth exceeding 110 GHz. The design methodology, theoretical analysis, and experimental results highlight the potential of InP DHBTs in enabling Tb/s-class optical transceivers and emerging applications like 6G wireless.

Reference

[1] R. Hersent et al., "InP DHBT Linear Modulator Driver With a 3-Vppd PAM-4 Output Swing at 90 GBaud: From Enhanced Transistor Modeling to Integrated Circuit Design," in IEEE Transactions on Microwave Theory and Techniques, vol. 72, no. 3, pp. 1618-1631, March 2024.

Comments